This article was downloaded by:

On: 14 January 2011

Access details: Access Details: Free Access

Publisher Taylor & Francis

Informa Ltd Registered in England and Wales Registered Number: 1072954 Registered office: Mortimer House, 37-

41 Mortimer Street, London W1T 3JH, UK

### **Molecular Simulation**

Publication details, including instructions for authors and subscription information: http://www.informaworld.com/smpp/title~content=t713644482

# A compact model for the ballistic subthreshold current in ultra-thin independent double-gate MOSFETs

D. Munteanu<sup>a</sup>; M. Moreau<sup>a</sup>; J. L. Autran<sup>ab</sup>

<sup>a</sup> Institute Materials Microelectronics Nanoscience of Provence (IM2NP, UMR CNRS 6242) Bâtiment IRPHE, Marseille Cedex 13, France <sup>b</sup> Institut Universitaire de France, Paris, France

To cite this Article Munteanu, D. , Moreau, M. and Autran, J. L.(2009) 'A compact model for the ballistic subthreshold current in ultra-thin independent double-gate MOSFETs', Molecular Simulation, 35: 6, 491-497

To link to this Article: DOI: 10.1080/08927020902801548 URL: http://dx.doi.org/10.1080/08927020902801548

# PLEASE SCROLL DOWN FOR ARTICLE

Full terms and conditions of use: http://www.informaworld.com/terms-and-conditions-of-access.pdf

This article may be used for research, teaching and private study purposes. Any substantial or systematic reproduction, re-distribution, re-selling, loan or sub-licensing, systematic supply or distribution in any form to anyone is expressly forbidden.

The publisher does not give any warranty express or implied or make any representation that the contents will be complete or accurate or up to date. The accuracy of any instructions, formulae and drug doses should be independently verified with primary sources. The publisher shall not be liable for any loss, actions, claims, proceedings, demand or costs or damages whatsoever or howsoever caused arising directly or indirectly in connection with or arising out of the use of this material.

# A compact model for the ballistic subthreshold current in ultra-thin independent double-gate MOSFETs

D. Munteanu<sup>a</sup>\*, M. Moreau<sup>a</sup> and J.L. Autran<sup>ab</sup>

<sup>a</sup>Institute Materials Microelectronics Nanoscience of Provence (IM2NP, UMR CNRS 6242) Bâtiment IRPHE, 49 rue Joliot-Curie, BP 146, F-13384 Marseille Cedex 13, France; <sup>b</sup>Institut Universitaire de France, Paris, France

(Received 21 October 2008; final version received 24 February 2009)

We present an analytical model for the subthreshold characteristic of ultra-thin independent double-gate (IDG) MOSFETs working in the ballistic regime. This model takes into account short-channel effects, quantisation effects and source-to-drain tunnelling (Wentzel-Kramers-Brillouin (WKB) approximation) in the expression of the subthreshold drain current. Important device parameters, such as off-state current or subthreshold swing, can be easily evaluated through this full analytical approach. The model can be successfully implemented in a Technologies Computer-Aided Design (TCAD) circuit simulator for the simulation of IDG MOSFET-based circuits.

Keywords: independently driven double-gate MOSFET; ballistic transport; quantum effects; subthreshold current model

#### 1. Introduction

Double-gate (DG) MOSFETs are extensively investigated because of their promising performances with respect to the International Technology Roadmap for Semiconductors (ITRS) specifications for deca-nanometre channel lengths. The main advantage of this architecture is to offer a reinforced electrostatic coupling between the conduction channel and the gate electrode. A DG structure can efficiently sandwich the semiconductor element playing the role of the transistor channel, which can be a silicon thin layer or nanowire, a carbon nanotube, a molecule or an atomic linear chain [1]. In spite of excellent electrical performances due to its multiple conduction surfaces, a conventional DG MOSFET allows only three-terminal operation because the two gate electrodes, i.e. the front gate and the back gate, are generally tied together. DG structures with independent gates have been proposed [2,3], having a four-terminal operation. Independent DG (IDG) MOSFETs offer additional potentialities, such as a dynamic threshold voltage control by one of the two gates, transconductance modulation and signal mixer, in addition to the conventional switching operation. Thus, IDG MOSFETs are promising for future high performance and low power consumption very large-scale integrated circuits. However, one of the identified challenges for IDG MOSFET optimisation remains the development of compact models [4–7] taking into account the main physical phenomena (such as short-channel effects, quantum confinement and ballistic transport) governing the devices at this scale of integration. In this work, an analytical subthreshold model of ultra-thin IDG MOSFETs working in the ballistic regime is presented. The present approach captures the essential physics of such ultimate devices: short-channel effects, quantum confinement, thermionic current and tunnelling of carriers through the source-to-drain barrier. Important device parameters, such as the off-state current ( $I_{\rm off}$ ) or the subthreshold swing, can be easily evaluated through this full analytical approach that also provides a complete set of equations for developing equivalent-circuit model used in ICs simulation.

### 2. Physics of the ballistic transport

In nanoscale MOSFETs with channel lengths less than about 50 nm, the relaxation times of the carriers indicate that the drain current will have an intermediate character between drift—diffusion and ballistic/quasi-ballistic transport [8]. Then, ballistic transport has to be considered in the modelling of ultra-short DG devices. Since the conventional drift—diffusion model (usually used in device simulation) fails to describe ballistic transport, new specific models have to be developed this regime.

The highest value of the source-to-drain current, which can be obtained for a given MOSFET geometry, corresponds to the pure ballistic current limit. As the channel length is increased, the current decreases from this maximum value due to scattering effects. The transport makes a transition from the ballistic to quasi-ballistic or drift-diffusion regime with the longer channel lengths [9]. The carrier transport in the channel is considered to be ballistic when carriers travel from the source to the drain regions without encountering a scattering event. This may be possible if the feature size of the device becomes smaller than the carrier mean free path

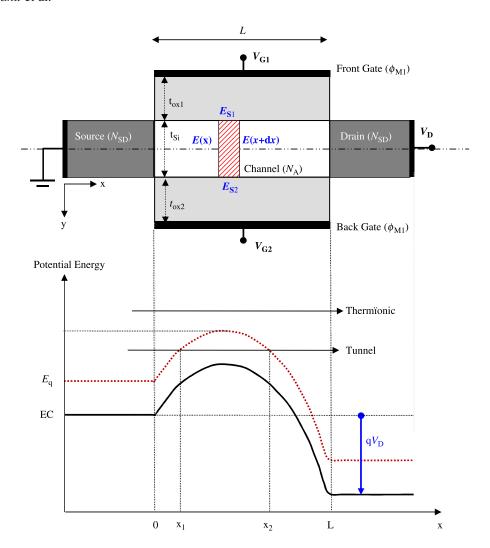

Figure 1. Schematic ultra-thin IDG MOSFET and its technological and electrical parameters considered in this work. The first energy subband profile  $E_1(x)$  obtained from Equation (11) is also represented (dotted line).

[10]. If the carrier transport is purely ballistic in the channel, modelling the device behaviour reduces to the description of the carrier transmission over and through the source-to-drain potential barrier [11]. The amplitude and the width of the channel barrier are modulated by the front-gate, the backgate and drain voltages. As explained in [11] and shown in Figure 1, carriers having energies higher than the maximum of the barrier are transmitted from source to drain by thermionic emission, while carrier with lower energy can traverse the channel only by quantum-mechanical (QM) tunnelling through the source-to-drain barrier.

# 3. Drain current modelling

## 3.1 Potential profile in the subthreshold regime

The model proposed here is developed for ultra-thin silicon film IDG MOSFETs working in the subthreshold regime. Figure 1 shows the schematic *n*-channel IDG MOSFET considered in this work. Carrier transport in the ultra-thin

silicon film (thickness  $t_{\rm Si}$ ) is considered 1D in the x-direction and the resulting current is controlled by both the front and back gate-to-source ( $V_{\rm G1}$  and  $V_{\rm G2}$ ) and drainto-source ( $V_{\rm D}$ ) voltages that impact the shape as well as the amplitude of the source-to-drain energy barrier. In the subthreshold regime, minority carriers can be neglected and Poisson's equation is analytically solved in the x-direction with explicit boundary conditions at the two oxide/silicon interfaces taking into account the electrostatic influence of  $V_{\rm G1}$  and  $V_{\rm G2}$ . We define the electrostatic potential  $\psi$  as the band bending with respect to the intrinsic Fermi level in the silicon film and choosing the Fermi level in the source reservoir as the potential reference. The expression of  $\psi(x)$  is obtained by applying the Gauss's law to the particular closed dashed surface shown in Figure 1 [12]:

$$-E(x)\frac{t_{Si}}{2} + E(x + dx)\frac{t_{Si}}{2} - E_{S1}(x) + E_{S2}(x) = -\frac{qN_A t_{Si} dx}{2\varepsilon_{Si}},$$

(1)

where  $N_A$  is the channel doping, and  $E_{S1}$  and  $E_{S2}$  are the electric fields at the front and back interfaces, respectively.  $E_{S1}$  and  $E_{S2}$  are given by:

$$E_{\rm S1} = \frac{\varepsilon_{\rm ox}}{\varepsilon_{\rm Si}} \frac{V_{\rm G1} - V_{\rm FB1} - \psi}{t_{\rm ox}},\tag{2}$$

$$E_{\rm S2} = -\frac{\varepsilon_{\rm ox}}{\varepsilon_{\rm Si}} \frac{V_{\rm G2} - V_{\rm FB2} - \psi_b}{t_{\rm ox}},\tag{3}$$

where  $\psi$  and  $\psi_b$  are the surface potentials at the front and back oxide/film interfaces, respectively. Due to the 1D character of the electrostatic potential  $\psi$  in the silicon film the electric field E(x) can be approximated as  $E(x) \approx -(\mathrm{d}\psi(x)/\mathrm{d}x)$  [13]. Using the development presented in [14], and after some algebraic manipulations, we obtained the following differential equation for the electrostatic potential in the silicon film:

$$\frac{\mathrm{d}^2 \Psi}{\mathrm{d}x^2} - \frac{2C_{\text{ox}}}{\varepsilon_{\text{Si}} t_{\text{Si}}} \Psi = \frac{1}{\varepsilon_{\text{Si}} t_{\text{Si}}} [q N_{\text{A}} t_{\text{Si}} - 2C_{\text{ox}} (V_{\text{G1}} - V_{\text{FB1}} - \phi_{\text{F}}) - 2C_{\text{ox}} (V_{\text{G2}} - V_{\text{FB2}} - \phi_{\text{F}})], \tag{4}$$

where  $V_{\rm FB1}$  and  $V_{\rm FB2}$  are the flat-band voltages at the frontand back-gate interfaces, respectively;  $\phi_{\rm F}$  is the bulk potential of the Silicon film; and  $C_{\rm ox} = \varepsilon_{\rm ox}/t_{\rm ox}$  is the gate capacitance per unit area. The analytical solution of Equation (4) can be then expressed in the form:

$$\psi(x) = C_1 \exp(\alpha x) + C_2 \exp(-\alpha x) - \frac{R}{\alpha^2}, \quad (5)$$

where the coefficients  $C_1$  and  $C_2$  are given by:

$$C_{1} = \frac{\phi_{S}[1 - \exp(-\alpha L)] + V_{D} + R((1 - \exp(-\alpha L))/\alpha^{2})}{2\sinh(\alpha L)},$$

(6)

$$C_2 = -\frac{\phi_S[1 - \exp{(\alpha L)}] + V_D + R((1 - \exp{(\alpha L)})/\alpha^2)}{2\sinh{(\alpha L)}},$$

with:

$$R = \frac{1}{\varepsilon_{\text{Si}} t_{\text{Si}}} \left( q N_{\text{A}} t_{\text{Si}} - 2 C_{\text{ox}} (V_{\text{G1}} - V_{\text{FB1}}) \frac{\gamma t_{\text{ox}} + t_{\text{Si}}}{2 \gamma t_{\text{ox}} + t_{\text{Si}}} - 2 C_{\text{ox}} (V_{\text{G2}} - V_{\text{FB2}}) \frac{\gamma t_{\text{ox}}}{2 \gamma t_{\text{ox}} + t_{\text{Si}}} \right),$$

(8)

$$\alpha = \sqrt{\frac{2C_{\text{ox}}}{\varepsilon_{\text{Si}}t_{\text{Si}}}},\tag{9}$$

$$\phi_S = \frac{kT}{q} \ln \left( \frac{N_{\rm A} N_{\rm SD}}{n_i^2} \right),\tag{10}$$

$$\phi_{\rm F} = \frac{kT}{q} \ln \left( \frac{N_{\rm A}}{n_i} \right),\tag{11}$$

where  $N_{\rm SD}$  is the doping level in the source and drain regions.

## 3.2 Quantum confinement effects

QM confinement of inversion-layer carriers are well known to significantly affect the threshold voltage and gate capacitance of highly scaled bulk and DG MOSFETs. The aggressive scaling down of MOSFETs in the deep submicrometre domain requires ultra-thin oxides and high channel doping levels for minimising the drastic increase of short-channel effects. The direct consequence is a strong increase in the electric field at the Si/SiO<sub>2</sub> interface, which creates a sufficiently steep potential well for inducing the quantisation of carrier energy. In bulk-Si and partially depleted SOI (n)MOSFETs, the confinement is in the potential well defined by the gate-oxide barrier (which is virtually infinite) and the silicon conduction (or valence) band. Carriers are then confined to a vertical direction in a quantum well (formed by the silicon conduction band bending at the interface and the oxide/silicon conduction band offset) having feature size close to the electron wavelength. This gives rise to a splitting of the energy levels into subbands (two-dimensional (2D) density of states) [15,16], such that the lowest of the allowed energy levels for electrons (resp. for holes) in the well does not coincide with the bottom of the conduction band (resp. the top of the valence band). In addition, the total densityof-states in a 2D system is less than that in a threedimensional (3D, or classical) system, especially for low energies. Carriers occupying the lowest energy levels behave like quantised carriers while those lying at higher energies, which are not as tightly confined to the potential well, can behave like classical (3D) particles with three degrees of freedom. As the surface electric field increases, the system becomes more quantised as more and more carriers become confined to the potential well. The QM confinement considerably modifies the carrier distribution in the channel: the maximum of the inversion charge is shifted away from the interface into the silicon film.

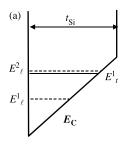

In thin-film IDG MOSFETs, the potential well is defined by both the front and back gates [17]. In these devices, carriers are confined due to two main phenomena (Figure 2): (a) strong electric field at the interface leading to electric field-induced quantum confinement (EC-QM) and (b)  $t_{\rm Si}$ -induced structural quantum confinement (SC-QM) due to the narrow potential well defined by thin silicon film. Since carriers in thin-film IDG MOSFETs are subjected to structural confinement, in addition to the EC-QM, QM effects on the threshold voltage and drain current are quite important [18,19].

If the silicon film in the IDG MOSFETs is thinner than 15 nm [19], quantum confinement cannot be ignored, and Poisson's equation should be solved self-consistently with

Electric field-induced confinement (EC-QM)

Structural confinement (SC-QM)

Figure 2. Energy-band diagrams in a vertical cross section in the Silicon film of IDG n-channel MOSFETs showing two possible cases of carrier confinement: (a) EC-QM and (b)  $t_{\rm Si}$ -induced SC-QM due to the narrow potential well defined by the thin silicon film.  $E_{\ell,\rm t}^i$  are the energy levels of the potential well ( $\ell$  corresponds to the longitudinal effective mass,  $m_\ell = 0.98 \times m_0$ , and t corresponds to the transversal effective mass,  $m_{\rm t} = 0.19 \times m_0$ ).

Schrödinger's equation. In this case, an analytical solution is not possible without making assumptions of the shape of either the potential distribution or the electron distribution [20]. When an IDG MOSFET is considered to work in the weak inversion regime (and the free-carrier term in the Poisson's equation can be neglected), the quantum energy levels can be calculated using the expressions developed in [20] using a variational approach. Considering the limit case of an ultra-thin silicon film, we can assume only one energy subband for the vertical confinement of carriers, given by [20]:

$$E_q \cong \left(\frac{\hbar^2}{2m_\ell}\right) \times \left[\left(\frac{\pi}{t_{\rm Si}}\right)^2 + A_\ell^2 \times \left(3 - \frac{4}{3} \frac{1}{1 + (A_\ell t_{\rm Si}/\pi)^2}\right)\right],\tag{12}$$

$$A_{\ell} \cong \left(\frac{3}{4} \times \frac{2m_{\ell} q E_x}{\hbar^2}\right)^{1/3} \tag{13}$$

where  $m_{\ell}$  is the electron longitudinal effective mass (vertical confinement) and  $E_x$  is the (spatially constant) transverse electric field in the ultra-thin body silicon film, dependent on the front- and back-gate voltage differences [20]:

$$E_x = -\frac{(V_{\text{FB1}} - V_{\text{FB2}}) - (V_{\text{G1}} - V_{\text{G2}})}{t_{\text{Si}} + 2(\varepsilon_{\text{Si}}/\varepsilon_{\text{ox}})t_{\text{ox}}}.$$

(14)

The first energy subband profile  $E_1(x)$  can be easily derived as:

$$E_1(x) = q(\phi_S - \psi(x)) + E_a$$

(15)

# 3.3 Ballistic current modelling in the ballistic subthreshold regime

Once  $E_1(x)$  is known as a function of  $V_{G1}$ ,  $V_{G2}$  and  $V_D$ , the total ballistic current (per device width unit) can be evaluated as follows:

$$I_{\rm DS} = I_{\rm Therm} + I_{\rm Tun},\tag{16}$$

where  $I_{\text{Therm}}$  and  $I_{\text{Tun}}$  are the thermionic and tunnelling components of the ballistic current, respectively. For a 2D gas of electrons [21],  $I_{\text{Therm}}$  and  $I_{\text{Tun}}$  are given by:

$$I_{\text{Therm}} = \frac{2q}{\pi^2 \hbar} \int_{-\infty}^{+\infty} dk_z \times \int_{E_{1,\text{max}}}^{+\infty} [f(E, E_{\text{FS}}) - f(E, E_{\text{FD}})] dE_x,$$

(17)

$$I_{\text{Tun}} = \frac{2q}{\pi^2 \hbar} \int_{-\infty}^{+\infty} dk_z \times \int_{0}^{E_{1,\text{max}}} [f(E, E_{\text{FS}}) - f(E, E_{\text{FD}})] T(E_x) dE_x,$$

(18)

where  $f(E_{\rm F}, E_{\rm FS})$  is the Fermi–Dirac distribution function;  $E_{\rm FS}$  and  $E_{\rm FD}$  are the Fermi level in the source and drain reservoirs, respectively ( $E_{\rm FD} = E_{\rm FS} - qV_{\rm DS}$ );  $k_z$  is the electron wave vector component in the z-direction; the factor 2 accounts for the two silicon valleys characterised by  $m_\ell$  in the confinement direction (y-direction); and  $T(E_x)$  is the barrier transparency for electrons; and E is the total energy of carriers in source and drain reservoirs given by:

$$E = E_1 + E_x + \frac{\hbar^2 k_z^2}{2m_t},\tag{19}$$

where  $E_1$  is the energy level of the first subband (given by Equation (15));  $E_x$  is the carrier energy in the direction of the current; and  $m_t$  is the electron transverse effective mass. In Equations (17) and (18),  $E_{1,\text{max}}$  is the maximum of the source-to-drain energy barrier given by:

$$E_{1,\text{max}} = E_1(x_{\text{max}}), \tag{20}$$

where  $x_{\text{max}}$  is obtained from Equation (4) with the condition:

$$\frac{\mathrm{d}\psi(x)}{\mathrm{d}x} = 0 \quad \text{for } x = x_{\text{max}},\tag{21}$$

$$x_{\text{max}} = \frac{1}{2\alpha} \ln \left( \frac{C_2}{C_1} \right). \tag{22}$$

In Equation (18), the barrier transparency is calculated using the WKB approximation:

$$T(E_x) = \exp\left(-2\int_{x_1}^{x_2} \sqrt{\frac{2m_t(E_1(x) - E_x)}{\hbar^2}} \, dx\right)$$

$$T_{\text{WKB}}(E_x > E_{1,\text{max}}) = 1,$$

(23)

•

where  $x_1$  and  $x_2$  are the coordinates of the turning points (Figure 1).  $x_1$  and  $x_2$  have literal expressions due to the analytical character of the barrier:

$$x_{1,2}(E_x) = \frac{1}{\alpha} \ln \left[ \frac{A \pm \sqrt{\Delta}}{2C_1} \right], \tag{24}$$

where the quantities A and  $\Delta$  are defined as follows:

$$A = \phi_S + \frac{R}{\alpha^2} + \frac{E_q}{q} - \frac{E_x}{q},\tag{25}$$

$$\Delta = A^2 - 4C_1C_2. \tag{26}$$

The WKB approximation has the main advantage to be central processing unit (CPU) inexpensive and reasonably accurate for channel lengths down to a few nanometres. Moreover, it has been shown in [22] that differences between results obtained considering the WKB approximation and full quantum treatment (tight-binding scheme) are surprisingly small (typically a few percents), which confers to the WKB approach a reasonable accuracy in the frame of the present analysis. The proposed model applies to (100) silicon inversion layers, but it can be extended to different crystal orientations or channel materials.

#### Results and model validation

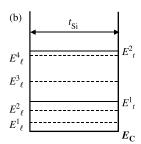

Figure 3 shows the first energy subband profile in the Si film calculated with the model in an  $L = 10 \,\mathrm{nm}$  intrinsic channel IDG MOSFET ( $t_{Si} = 2 \text{ nm}, t_{ox} = 0.6 \text{ nm}$ ). In order to test the validity of the model, we compare these profiles with those obtained with a self-consistent Poisson-Schrödinger solver based on a real-space non-equilibrium Green's function approach (DGGREEN2D [23]).

Figure 3. First energy subband profiles  $E_1(x)$  in the Silicon film calculated with the analytical model (Equation (13)) and with the 2D numerical code DGGREEN2D [23]. Device parameters are:  $L = 10 \,\mathrm{nm}$ ,  $t_{\mathrm{Si}} = 2 \,\mathrm{nm}$  and  $t_{\mathrm{ox}} = 0.6 \,\mathrm{nm}$ .

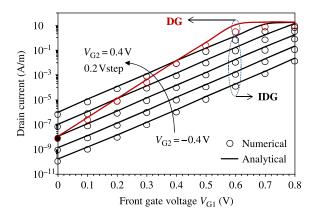

Figure 4. Subthreshold  $I_D(V_{G1})$  characteristics calculated with the analytical model (lines). Values obtained with the 2D numerical code DGGREEN2D [23] are also reported for comparison (symbols). Device parameters are the same as in Figure 3.

As shown in Figure 3, a good agreement is obtained between the two barriers in the subthreshold regime. In particular, we note an excellent agreement for the positions of the maximum as well as the amplitude of the barrier between the analytical and numerical curves. The slight difference in the barrier width is due to the electric field penetration in the source and drain regions, only taken into account of the numerical approach.

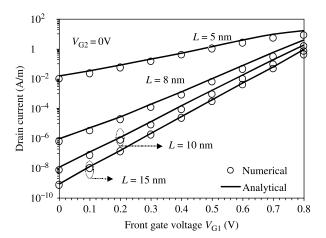

The subthreshold  $I_D(V_{G1})$  characteristics calculated with the analytical model for IDG MOSFET with L = 10 nm and different back-gate voltages are shown in Figure 4. Drain current characteristics for DG MOSFETs are also shown in this figure. Figure 5 compares analytical model and numerical data for IDG MOSFET with different channel lengths. These figures show that, in the subthreshold regime, the analytical model very well fits numerical data obtained with DGGREEN2D for devices in the deca-nanometre range.

Figure 5.  $I_D(V_{G1})$  characteristics of IDG MOSFET calculated with the analytical model. Values obtained with the 2D numerical code DGGREEN2D [23] are also reported for comparison. Device parameters are:  $t_{Si} = 2 \text{ nm}$  and  $t_{ox} = 0.6 \text{ nm}$ .

# 5. Discussion: impact of the source-to-drain tunnelling current

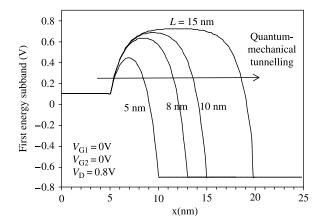

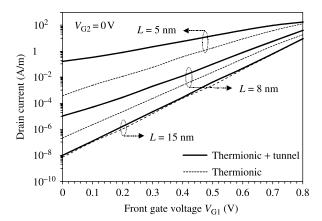

QM tunnelling was often neglected in several previous works, which mainly focused on the modelling of thermionic emission or scattering [24,25]. However, below 8 nm, the width of the channel barrier decreases significantly (Figure 6), increasing the impact of the quantum tunnelling on the device characteristics. We have analyzed the impact of carrier tunnelling on device performances through a detailed comparison between model predictions with and without QM tunnelling. Two cases are considered: (1) thermionic emission for  $E_x > E_{\text{max}}$ and  $T(E_x) = 0$  for  $E_x < E_{\text{max}}$  and (2) thermionic emission for  $E_x > E_{\text{max}}$  and quantum tunnelling with  $T(E_x)$  given by the WKB approximation (Equation (23)). Figure 7 shows subthreshold  $I_D(V_{G1})$  drain current characteristics calculated with the analytical model for channel lengths from 5 to 15 nm. Two series of curves have been plotted, considering or not the WKB tunnelling contribution in the ballistic current. These results highlight the dramatic impact of the source-to-drain tunnelling current on the subthreshold slope and also on the off-state current. In such a subthreshold regime, the carrier transmission by thermionic emission is reduced or even suppressed due to the high channel barrier. As a consequence, when the channel length decreases, the tunnelling becomes dominant and constitutes the main physical phenomenon limiting the devices scaling, typically below channel lengths of  $\sim 8$  nm. QM tunnelling significantly degrades the off-state current especially in short channels, where the off-state current increase by more than two decades ( $L_{\rm g}=5\,{\rm nm}$ ). However, the off-state current should be slightly reduced for the shorter geometries since it is calculated assuming perfectly ballistic transport and thus ignoring the partial reflection of electron wave functions on the source barrier. The subthreshold swing also increases (with about 30% for  $L_{\rm g}=8\,{\rm nm}$  with respect to  $L=15\,{\rm nm}$ )

Figure 6. Variation of the source-to-drain energy barrier in the channel when decreasing the channel length ( $V_{\rm G1}=V_{\rm G2}=0\,{\rm V}$ ,  $V_{\rm D}=0.8\,{\rm V}$ ). Device parameters are the same as in Figure 5.

Figure 7. Subthreshold  $I_{\rm D}(V_{\rm GI})$  characteristics calculated with the analytical model when considering or not the WKB tunnelling component in the ballistic current. Device parameters are the same as in Figure 5.

due to QM tunnelling. As previously indicated for the offstate current, these results can be considered as an upper limit, since we assume perfectly ballistic transport without wave function reflection at the source barrier.

#### 6. Conclusion

An analytical model for the subthreshold drain current in ultra-thin IDG MOSFETs working in the ballistic regime is presented. The model is particularly well adapted for ultra-short IDG transistors in the deca-nanometre scale since it accounts for the main physical phenomena related to these ultimate devices: 2D short-channel effects, quantum vertical confinement as well as carrier transmission by both thermionic emission and quantum tunnelling through the source-to-drain barrier. The model is used to predict the variation with the channel length of essential subthreshold parameters, such as the off-state current and the subthreshold slope.

### Acknowledgements

This work was supported by the French Ministry of Research (ANR PNANO project 'MULTIGRILLES').

#### References

- [1] M. Bescond, J.L. Autran, D. Munteanu, and M. Lannoo, *Atomic-scale modeling of double-gate MOSFETs using a tight-binding Green's function formalism*, Solid State Electron. 48 (2004), pp. 567–574.

- [2] M. Masahara, Y. Liu, K. Sakamoto, K. Endo, T. Matsukawa, K. Ishii, T. Sekigawa, H. Yamauchi, H. Tanoere, S. Kanemaru et al., Demonstration, analysis, and device design considerations for independent DG MOSFETs, IEEE Trans. Electron. Devices 52 (2005), pp. 2046–2051.

- [3] L. Mathew, Y. Du, A.V. Thean, M. Sadd, A. Vandooren, C. Parker, T. Stephens, R. Mora, R. Rai, M. Zavala et al., *CMOS vertical multiple independent gate field effect transistor (MIGFET)*, Proc. IEEE Int. SOI Conference (2004), pp. 187–189.

- [4] W. Zhang, J.G. Fossum, L. Mathew, and Y. Du, Physical insights regarding design and performance of independent-gate FinFETs, IEEE Trans. Electron. Devices 52 (2005), pp. 2198-2206.

- [5] G. Pei and E.C. Kan, Independently driven DG MOSFETs for mixedsignal circuits: part I - quasi-static and nonquasi-static channel coupling, IEEE Trans. Electron. Devices 51 (2004), pp. 2086-2093.

- [6] G. Pei, W. Ni, A.V. Kammula, B.A. Minch, and E.C. Kan, A physical compact model of DG MOSFET for mixed-signal circuit applications - part I: model description, IEEE Trans. Electron. Devices 50 (2003), pp. 2135-2143.

- [7] D. Munteanu, J.L. Autran, X. Loussier, S. Harrison, R. Cerutti, and T. Skotnicki, Quantum short-channel compact modeling of draincurrent in double-gate MOSFET, Solid State Electron. 50 (2006), pp. 680-686

- [8] B. Iñiguez, T.A Fjedly, A. Lázaro, F. Danneville, and M.J Deen, Compact-modeling solutions for nanoscale double-gate and gateall-around MOSFETs, IEEE Trans. Electron. Devices 53 (2006),

- [9] S. Martinie, G. Le Carval, D. Munteanu, S. Soliveres, and J.L. Autran, Impact of ballistic and quasi-ballistic transport on performances of double-gate MOSFET-based circuits, IEEE Trans. Electron. Devices 55 (2008), pp. 2443-2453.

- [10] M. Lundstrom, J.L. Autran, X. Loussier, S. Harrison, and R. Cerutti, Fundamentals of Carrier Transport, 2nd ed., Cambridge University Press, Cambridge, 2000.

- D. Munteanu and J.L. Autran, Two-dimensional modeling of quantum ballistic transport in ultimate double-gate SOI devices, Solid State Electron. 47 (2003), pp. 1219-1225.

- [12] D. Munteanu, J.L. Autran, X. Loussier, S. Harrison, and R. Cerutti, Compact modeling of symmetrical double-gate MOSFETs including carrier confinement and short-channel effects, Mol. Simul. 33 (2007), pp. 605–611.

- [13] D. Munteanu, J.L Autran, S. Harison, K. Nehari, O. Tintori, and T. Skotnicki, Compact model of the quantum short-channel threshold voltage in symmetric double-gate MOSFET, Mol. Simul. 31 (2005), pp. 831-837.

- [14] D. Munteanu, J.L. Autran, X. Loussier, and O. Tintori, Compact modeling of drain current in independently driven double-gate

- MOSFETs, in Proc. International NSTI Nanotech Conference -Workshop on Compact Modeling, 2007, pp. 574-577.

- [15] Y. Taur and T.H. Ning, Fundamentals of Modern VLSI Devices, Cambridge University Press, Cambridge, 1998.

- [16] S.A. Hareland, S. Jallepalli, W.-K. Shih, H. Wang, G.L. Chindalore, A.F. Tasch, and C.M. Maziar, A physically-based model for quantization effects in hole inversion layers, IEEE Trans. Electron. Devices 45 (1998), pp. 179-186.

- [17] T. Ernst, D. Munteanu, S. Cristoloveanu, T. Ouisse, S. Horiguchi, Y. Ono, Y. Takahashi, and K. Murase, Investigation of SOI MOSFETs with ultimate thickness, Microelectron. Eng. 48 (1999), pp. 339-342.

- [18] V. Trivedi and J.G. Fossum, Quantum-mechanical effects on the threshold voltage of undoped double-gate MOSFETs, IEEE Electron. Dev. Lett. 26 (2005), pp. 579–582.

- [19] M. Moreau, D. Munteanu, and J.L. Autran, Simulation analysis of quantum confinement and short-channel effects in independent double-gate metal-oxide-semiconductor field-effect transistors, Jpn. J. Appl. Phys. 47 (2008), pp. 7013-7018.

- [20] L. Ge and J.G. Fossum, Analytical modeling of quantization and volume inversion in thin Si-film DG MOSFETs, IEEE Trans. Electron. Devices 49 (2002), pp. 287-294.

- [21] D.K. Ferry and S.M. Goodnick, Tranport in Nanostructures, Cambridge University Press, Cambridge, 1997.

- [22] M. Städele, Influence of source-drain tunneling on the subthreshold behavior of sub-10 nm double-gate MOSFETs, in Proc. European Solid-State Device Research Conference (ESSDERC), 2002, pp. 135-138.

- [23] J.L. Autran and D. Munteanu, Simulation of electron transport in nanoscale independent-gate double-gate devices using a full 2D Green's function approach, J. Comput. Theor. Nanosci. 5 (2008), pp. 1120-1127.

- [24] K. Natori, Ballistic metal-oxide-semiconductor field effect transistor, J. Appl. Phys. 76 (1994), pp. 4879-4890.

- [25] M.S. Lundstrom, Elementary scattering theory of the Si MOSFET, IEEE Electron Dev. Lett. 18 (1997), pp. 361-363.